ARM cortex Cache managment

ling Instruction and Data Cache

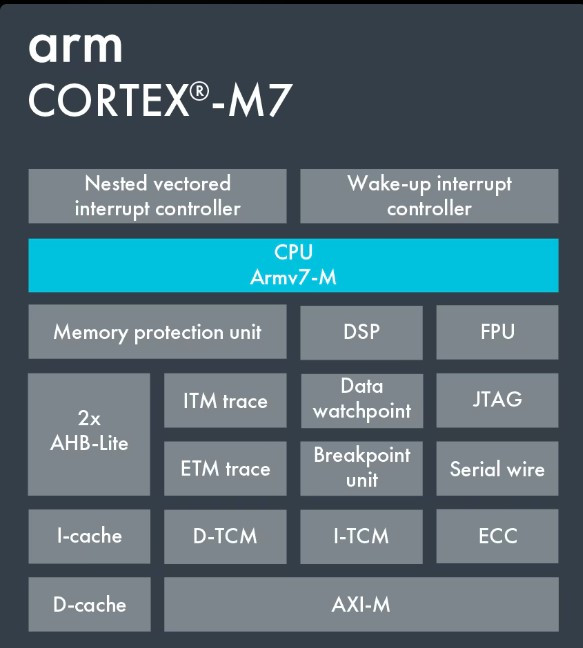

The ARM Cortex-M7 microcontroller architecture is designed to enhance performance in embedded systems, particularly in real-time applications. A key feature of this architecture is its cache system, which includes separate instruction and data caches (I-Cache and D-Cache). This blog will explore how to enable these caches, their significance, and best practices for their management.

Cache Architecture Overview:

The ARM Cortex-M7 employs a Harvard architecture, which means it has distinct pathways for instruction fetches and data accesses. This separation allows simultaneous operations on both instruction and data, significantly improving throughput compared to a von Neumann architecture where a single bus is shared13.

Instruction Cache (I-Cache):

Purpose: The I-Cache is designed to store instructions fetched from memory, allowing the CPU to execute them more quickly. By keeping frequently used instructions in the cache, the system reduces the need for repeated accesses to slower main memory12.

Size and Structure: Typically, the I-Cache ranges from 16 KB to 64 KB and is usually 4-way set-associative with a line size of 32 bytes13.

Maintenance: Since the I-Cache is read-only, any changes to instructions require cache invalidation to ensure that the CPU fetches the latest instructions from memory. This maintenance is crucial when modifying code stored in flash memory26.

Data Cache (D-Cache):

Purpose: The D-Cache is a buffer for data read and write operations. It enables faster access to frequently used data by caching it close to the CPU56.

Size and Structure: Similar to the I-Cache, the D-Cache can vary in size but typically matches the I-Cache in capacity. It also employs a 4-way set-associative structure13.

Maintenance: Unlike the I-Cache, the D-Cache can be written to directly by the CPU. However, when data is modified, it must be cleaned (written back) to ensure that subsequent reads reflect the most current values26.

Enabling Caches:

To enable the instruction and data caches on an ARM Cortex-M7 device, specific architectural instructions must be followed. These typically involve manipulating control registers:

System Control Register (SCTLR):

Set the Instruction Cache Enable bit (I) to 1.

Set the Data Cache Enable bit (C) to 1.

Example configuration

SCTLR = (1 << 12) | (1 << 2); // Enable I-Cache and D-Cache

Initialization:

At system startup, both caches should be invalidated to ensure they start with no stale data or instructions.

Use Cortex Microcontroller software Interface Standard (CMSIS) functions for cache maintenance operations:

SCB_CleanInvalidateDCache(); // Clean and invalidate D-Cache

SCB_InvalidateICache(); // Invalidate I-Cache

Best Practices for Cache Management

To optimize performance when using caches in ARM Cortex-M7:

Understand Access Patterns: Recognize that instruction fetches are sequential while data accesses can be more random. Optimize your code structure accordingly37.

Frequent Maintenance: Regularly invalidate or clean caches when modifying code or data. This ensures that your application always operates on up-to-date information26.

Consider Multi-Master Systems: In systems with multiple masters (e.g., DMA controllers), ensure proper cache coherency to avoid stale reads/writes across different components8.

Conclusion

Enabling and effectively managing instruction and data caches in ARM Cortex-M7 devices can lead to significant performance improvements in embedded applications. By understanding the architecture, properly configuring control registers, and adhering to best practices for cache maintenance, developers can leverage these features for enhanced system efficiency and responsiveness.